基于FPGA的正弦信号发生器设计

【面向专业】

通信工程、生物医学工程

【所属课程】

数字逻辑与设计

【实验目标】

结合《数字逻辑与设计》理论课程,通过对实验测试理论的深入学习,将数字电路的各个单元模块进行合理组合,完成小型综合功能电路的设计,并熟练掌握查找与排除小型综合电路故障的方法,提高学生对数字电路的综合设计与测试能力。

【实验类型】

基本型

【实验意义】

自主学习数字电路逻辑与设计基础知识,增强学生对小型综合功能电路的设计和故障的排除。

【实验方式】

在Quartus II上完成七段数码管显示译码电路设计,并对该设计进行编辑、编译、综合、适配、仿真,最终给出其所有信号的时序仿真波形。

【教学流程及学习效果】

(1)在QuartusII上用VHDL文本方式设计七段数码管显示译码电路;

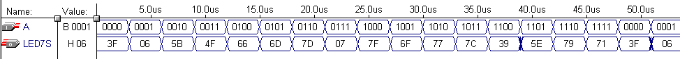

(2)对该设计进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。提示:用输入总线的方式给出输入信号仿真数据,仿真波形示例图如图所示。

(3)将经过仿真的设计下载到硬件实验箱进行验证。

图 七段译码器仿真波形

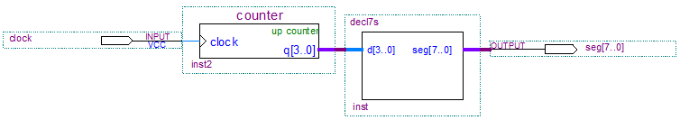

(4)添加4位计数器兆功能模块,按照图所示连接成顶层设计电路(用原理图方式),图中counter为4位计数器兆功能模块,模块DECL7S即为实验内容1设计的实体元件,注意图中的部分连接线是总线。用数码管8显示译码输出,时钟信号接CLOCK0。对该顶层工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。将经过仿真的设计下载到硬件实验箱进行验证。

图 顶层设计电路

其中兆功能模块添加步骤如下:

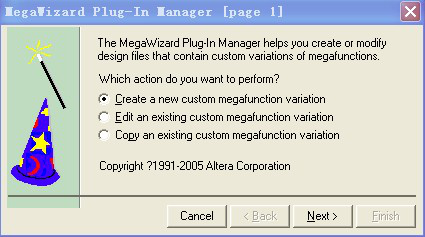

1)从[Tools]>>[Mega Wizard Plug-In Manager…]打开如图所示模块向导。选择【Creat a new custom megafunction variation】新建一个新的兆功能模块。

图 兆功能模块向导1

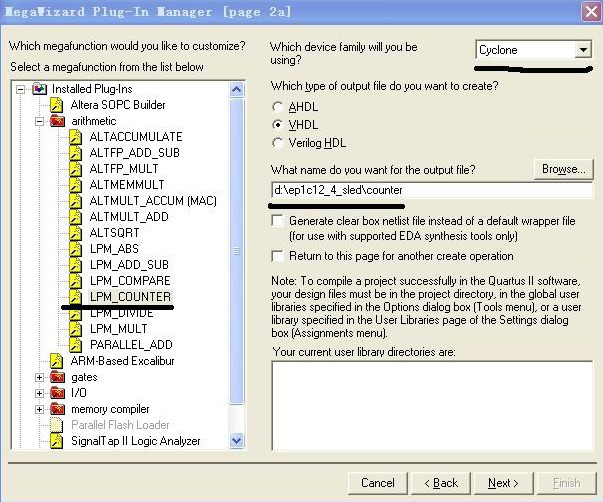

2)按NEXT 进入向导第二页,按照图所示选择和设置,注意标记处。

图 兆功能模块向导2

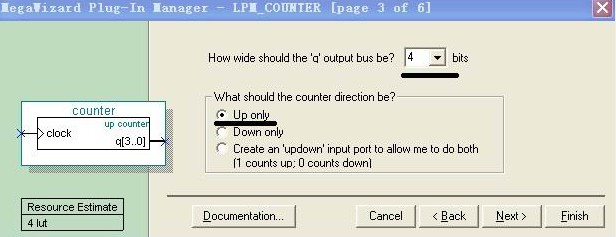

3) 按NEXT 进入向导第三页,按照图所示选择和设置,注意标记处。

图 兆功能模块向导3

4)在图中按NEXT进入向导第四页。第4页到第6页不用更改设置,直接按NEXT,最后按FINISH完成4位计数器兆功能模块的添加。

[引脚锁定]:

用键8~键5控制输入(引脚号:3,4,6,7),Clock0(引脚号为28)控制输入CLK,用第8位数码管输出(引脚号167,166,165,164,163,162,161)。